Hardware Demo Award für Team um CDNC-Doktorand Jonas Krautter

Der ehemaliger KIT-Informatikstudent und derzeitige Doktorand in der CDNC-Gruppe von Prof. Mehdi B. Tahoori erzielte mit seinem Team den dritten Platz der Hardware Demo Awards für ihre Präsentation mit dem Thema „Software-based Fault and Power Side-Channel Attacks inside Multi-Tenant FPGAs“. Gemeinsam mit Dr. Tahoori selbst und den beiden Kooperationspartnern Dr. Falk Schellenberg und Priv.-Doz. Dr. Amir Moradi der Ruhr Universität Bochum (RUB) schaffte es das Team aus insgesamt 31 Teilnehmern einen der begehrten Preise abzuräumen.

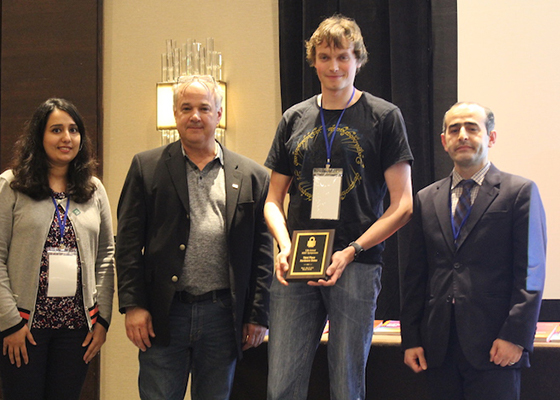

Die Personen auf dem Bild sind v.l.n.r: Fareena Saqib, University of North Carolina at Charlotte (Demo Chair); Prof. Jim Plusquellic, University of New Mexico (Awards Chair); Jonas Krautter, KIT; Hassan Salmani, Howard University (Demo Chair)

Den Kern des Projekts bilden Field-Programmable Gate Arrays (kurz: FPGAs), also generische Beschleuniger, die nach der Programmierung nahezu beliebige digitale Schaltungen realisieren können. Sie werden unter anderem auch zunehmend im Cloud-Computing, zum Beispiel bei Amazon AWS angeboten.

Interessant ist insbesondere in der Cloud die Virtualisierung dieser generischen Hardware-Beschleuniger. Dabei werden die Ressourcen des Chips in Partitionen aufgeteilt und diese wiederum unterschiedlichen Benutzern zur Verfügung gestellt. Problematisch ist hierbei, dass die verschiedenen Nutzer des FPGAs zwar auf logischer Ebene separiert sind, aber aufgrund der gemeinsamen Stromversorgung Angriffe auf der elektrischen Ebene möglich sind.

Drei Varianten solcher Angriffe präsentierte das Team bei einer Live-Demonstration und veranschaulichte, wie in wenigen Minuten geheime Schlüssel eines Verschlüsselungsmoduls auf einer Partition eines FPGAs durch einen isolierten Angreifer auf einer anderen Partition rekonstruiert werden können.

Das Bild zeigt die Demo sowie das Poster zur Präsentation.

Der Lehrstuhl für Zuverlässiges Nano-Computing (CDNC) ist Teil des ITEC – Institut für Computer Engineering. Der Forschungsschwerpunkt liegt auf dem Gebiet des zuverlässigen Computings im Nanobereich (Test und Zuverlässigkeit) und auf neuen Nanotechnologien für das Computing.

Das IEEE International Symposium on Hardware Oriented Security and Trust ist ein jährliches Symposium, das das schnelle Wachstum der hardwarebasierten Sicherheitsforschung und -entwicklung fördern soll. Es hat zum Ziel, das schnelle Wachstum der hardwarebasierten Sicherheitsforschung und -entwicklung zu fördern und neue Ergebnisse im Bereich der Hardware-Sicherheit hervorzuheben.

Genauere Informationen zu dem Projekt und der Demo finden Sie hier: https://cdnc.itec.kit.edu/SCA-DFA-Demo.php